Les portes logiques

I. Présentation :

La numération binaire comporte 2 états : 0 et 1.

Les opérateurs qui agissent sur les systèmes à 2 états sont dits logiques.

Grâce à ces opérateurs logiques simples, on peut réaliser les opérations les

plus complexes.

Techniquement ces opérations simples sont réalisées par des dispositifs électroniques

appelés portes logiques.

II. Les portes logiques :

Les portes logiques sont des circuits intégrés constitués par des transistors.

Les transistors fonctionnent avec une tension d'alimentation positive notée

VCC. Elles possèdent une ou plusieurs entrées et une seule sortie.

Les états des entrées et de la sortie sont caractérisés par des tensions de

type logique (0 ou Vcc ).

L'état de la sortie dépend de l'état des entrées.

Il existe deux types de technologie de portes logiques :

- La technologie TTL : transistor transistor logique

La tension d'alimentation VCC est de 5 V et le courant nécessaire

à la saturation des transistors est de l'ordre du mA: ce qui pose des problèmes

d'intégration (nombre de transistor par unité de surface). Les pertes par effet

Joule font chauffer le circuit ce qui nuit à son fonctionnement.

- La technologie CMOS : complementary metal-oxyde semi conductor

La tension d'alimentation VCC va de 3 V à 18 V et le courant nécessaire

à la saturation des transistors est de l'ordre du µA: ce qui permet une plus

grande intégration.

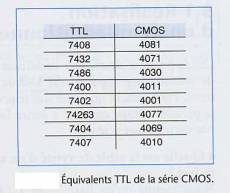

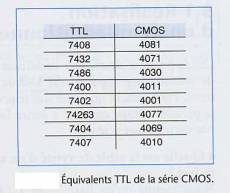

C'est la technologie CMOS qui a maintenant pris le pas sur la technologie TTL

Cependant pour certaines applications, la technologie TTL est préférée car son

temps de commutation est plus faible.

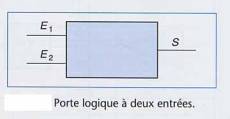

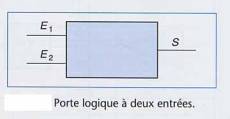

On utilise fréquemment des portes logiques

à 2 entrées E1 et E2. La sortie est notée S.

|

Plusieurs portes logiques de même type sont regroupées sur une même puce.

Le brochage est indiqué sur le schéma suivant :

|

|

|

|

|

Cette puce comporte 4 portes à deux entrées :

- les pattes 1-2-3 sont respectivement E1-E2-S pour

la première porte;

- les pattes 4-5-6 sont respectivement S-E2-E1 pour

la deuxième porte;

- les pattes 8-9-10 sont respectivement E1-E2-S

pour la troisième porte;

- les pattes 11-12-13 sont respectivement S-E2-E1

pour la quatrième porte;

La patte 14 sert à l'alimentation

La patte 7 est reliée à la masse

|

|

Dans toute la famille CMOS 4000, l’alimentation

se fait toujours entre les pattes 0 (0V) et 14 (Vcc).

Le circuit ci-contre comporte 4 portes logiques

à 2 entrées.

Par exemple, les pattes 12 et 13 constituent

les entrées correspondant à la sortie 11.

|

|

|

|

|

|

|

III. Le TP :

Le but du TP est d’étudier à l’aide d’une platine le comportement de différentes

portes logiques, d’en établir la table de vérité et de retrouver la fonction

associée à chaque code.

Pour étudier une porte logique, on réalisera le circuit suivant sur une

mini – platine :

|

Tension d'alimentation UA

= 5V continue.

Relier la masse de l'alimentation à la patte 7.

Placer un voltmètre aux bornes de l'alimentation.

l'état 1 des entrées E1 et E2 sera obtenu

pour U1 et U2 égales à UA

(pattes d'entrées reliées à l'alimentation avec UA =

5V)

l'état 0 des entrées E1 et E2 sera obtenu

pour U1 et U2 égales à 0

(pattes d'entrées reliées à la masse)

|

On mesurera la tension de sortie US

pour les différents cas.

La table de vérité regroupera tous les cas de figure.

|

Porte 4070

|

|

Porte 4071

|

|

Porte 4011

|

|

E1

|

E2

|

S

|

|

E1

|

E2

|

S

|

|

E1

|

E2

|

S

|

|

0

|

0

|

|

|

0

|

0

|

|

|

0

|

0

|

|

|

0

|

1

|

|

|

0

|

1

|

|

|

0

|

1

|

|

|

1

|

0

|

|

|

1

|

0

|

|

|

1

|

0

|

|

|

1

|

1

|

|

|

1

|

1

|

|

|

1

|

1

|

|

Traduire par une phrase simple utilisant des connecteurs logiques (et, ou,

ni, non) à quelles conditions la sortie est dans l’état 1.

Identifier les fonctions logiques réalisées par les portes.

Trouver les tables de vérité des portes et, non ou, non ou exclusif.

Simulation de portes logiques

avec Excel